- 您现在的位置:买卖IC网 > Sheet目录411 > EK43701-01 (Peregrine Semiconductor)KIT EVAL FOR 43701 RF DSA

�� �

�

PE43701�

�Product� Specification�

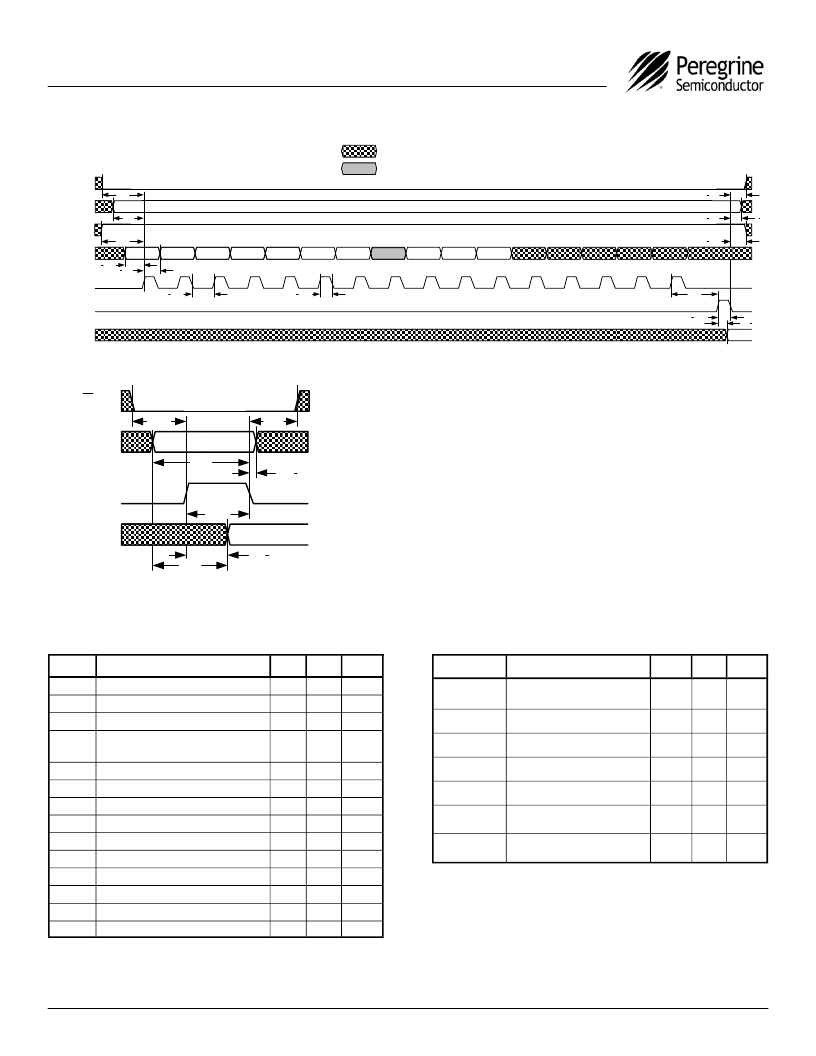

�Figure� 20.� Serial-Addressable� Timing� Diagram�

�Bits� can� either� be� set� to� logic� high� or� logic� low�

�*D[7]� must� be� set� to� logic� low�

�DI[6:0]�

�T� DISU�

�T� DIH�

�ADD[2:0]�

�VALID�

�P/S�

�T� ASU�

�T� PSSU�

�T� AIH�

�T� PSIH�

�SI�

�D[0]�

�D[1]�

�D[2]�

�D[3]�

�D[4]�

�D[5]�

�D[6]�

�*D[7]�

�A[0]�

�A[1]�

�A[2]�

�CLK�

�T� SISU�

�T� SIH�

�LE�

�T� CLKL�

�T� CLKH�

�T� LESU�

�DO[6:0]�

�Figure� 21.� Latched-Parallel/Direct-Parallel� Timing� Diagram�

�P/S�

�T� LEPW�

�T� PD�

�VALID�

�DI[6:0]�

�T� PSSU�

�VALID�

�T� PSH�

�LE�

�DO[6:0]�

�T� DISU�

�T� LEPW�

�T� DIPD�

�VALID�

�T� PD�

�T� DIH�

�Table� 11.� Serial-Addressable� Interface�

�AC� Characteristics�

�V� DD� =� 3.3� or� 5.0� V,� -40°� C� <� T� A� <� 85°� C,� unless� otherwise� specified�

�Table� 12.� Parallel� and� Direct� Interface�

�AC� Characteristics�

�V� DD� =� 3.3� or� 5.0� V,� -40°� C� <� T� A� <� 85°� C,� unless� otherwise� specified�

�Symbol�

�F� CLK�

�T� CLKH�

�T� CLKL�

�T� LESU�

�T� LEPW�

�T� SISU�

�T� SIH�

�T� DISU�

�T� DIH�

�T� ASU�

�Parameter�

�Serial� clock� frequency�

�Serial� clock� HIGH� time�

�Serial� clock� LOW� time�

�Last� serial� clock� rising� edge� setup�

�time� to� Latch� Enable� rising� edge�

�Latch� Enable� min.� pulse� width�

�Serial� data� setup� time�

�Serial� data� hold� time�

�Parallel� data� setup� time�

�Parallel� data� hold� time�

�Address� setup� time�

�Min�

�-�

�30�

�30�

�10�

�30�

�10�

�10�

�100�

�100�

�100�

�Max�

�10�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�Unit�

�MHz�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�Symbol�

�T� LEPW�

�T� DISU�

�T� DIH�

�T� PSSU�

�T� PSIH�

�T� PD�

�T� DIPD�

�Parameter�

�Latch� Enable� minimum�

�pulse� width�

�Parallel� data� setup� time�

�Parallel� data� hold� time�

�Parallel/Serial� setup� time�

�Parallel/Serial� hold� time�

�Digital� register� delay�

�(internal)�

�Digital� register� delay�

�(internal,� direct� mode� only)�

�Min�

�30�

�100�

�100�

�100�

�100�

�-�

�-�

�Max�

�-�

�-�

�-�

�-�

�-�

�10�

�5�

�Unit�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�T� AH�

�T� PSSU�

�T� PSH�

�T� PD�

�Address� hold� time�

�Parallel/Serial� setup� time�

�Parallel/Serial� hold� time�

�Digital� register� delay� (internal)�

�100�

�100�

�100�

�-�

�-�

�-�

�-�

�10�

�ns�

�ns�

�ns�

�ns�

�Note:�

�f� Clk� is� verified� during� the� functional� pattern� test.� Serial-�

�Addressable� programming� sections� of� the� functional�

�pattern� are� clocked� at� 10� MHz� to� verify� fclk� specification.�

�Document� No.� 70-0243-06� │� www.psemi.com�

�?2008-2009� Peregrine� Semiconductor� Corp.� All� rights� reserved.�

�Page� 9� of� 13�

�Logo� updated� under� non-rev� change.� Peregrine� products� are� protected� under� one� or� more� of� the� following� U.S.� Patents:� http://patents.psemi.com�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EK43702-01

KIT EVAL FOR PE43702 RF DSA

EK43703-01

KIT EVAL FOR PE43703 DSA

EK64904-01

KIT EVAL FOR 64904 NO CABLES

EK64905-11

KIT EVAL FOR 64904 W/CABLES

EKL3104

D-IMAGER 3D IMAGE SENSOR

EKL3105

3D IMAGE SENSOR-HIGH PRECISION

EKL3106

3D IMAGE SENSOR-HIGH PRECISION

EKMB1301111K

SENSOR PIR

相关代理商/技术参数

EK43702-01

功能描述:KIT EVAL FOR PE43702 RF DSA RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:UltraCMOS™, HaRP™ 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796

EK43703-01

功能描述:KIT EVAL FOR PE43703 DSA RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:UltraCMOS™, HaRP™ 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796

EK43704-11

制造商:Peregrine Semiconductor 功能描述:FREQUENCY CONTROL EVALUATION BOARD

EK43705-11

功能描述:EVAL KIT FOR RF DSA 7BIT 50OHM 制造商:peregrine semiconductor 系列:UltraCMOS?,HaRP?? 零件状态:有效 类型:衰减器 频率:50MHz ~ 8GHz 配套使用产品/相关产品:PE43705 所含物品:板 标准包装:1

EK43711-02

功能描述:EVAL BOARD FOR PE43711 制造商:peregrine semiconductor 系列:UltraCMOS?,HaRP?? 零件状态:有效 类型:衰减器 频率:9kHz ~ 6GHz 配套使用产品/相关产品:PE43711 所含物品:板 标准包装:1

EK43712-02

功能描述:EVAL BOARD FOR PE43712 制造商:peregrine semiconductor 系列:UltraCMOS?,HaRP?? 零件状态:有效 类型:衰减器 频率:9kHz ~ 6GHz 配套使用产品/相关产品:PE43712 所含物品:板 标准包装:1

EK43713-02

功能描述:EVAL BOARD FOR PE43713 制造商:peregrine semiconductor 系列:UltraCMOS?,HaRP?? 零件状态:有效 类型:衰减器 频率:9kHz ~ 6GHz 配套使用产品/相关产品:PE43713 所含物品:板 标准包装:1

EK4408X05XA-D5X WAF

制造商:Fairchild Semiconductor Corporation 功能描述: